最新文章

Xilinx工具可幫助選擇適合的存儲器陣列

降低靜態功率的另一個方法是仔細審查設計,避免冗余的直流消耗源。設計中經常會使用到具有多余或隱藏DCM或PLL的模塊,這種情況可能在模塊設計后忘記將多余的資源去除,或者在構建下一代產品時使用了一些遺留代碼。將DCM或PLL抽象到設計的頂層,這樣模塊之間就可以共享資源,從而可進一步減小設計的規模并降低直流功率。

更好地使用存儲器模塊也可幫助降低FPGA設計的動態功耗,從而進一步降低總體功耗。由于動態功耗是容抗(面積或長度)和頻率的函數,因此應當檢查設計中訪問塊存儲器的方式并確定能夠對容抗和頻率進行優化的區域。

Xilinx FPGA提供兩種類型的存儲器陣列。18Kbit或36Kbit的BRAM是針對大存儲器模塊而優化的。LUTRAM基于FPGA中的查找表,是針對細粒度存儲而優化的。Xilinx Virtex-5 FPGA中,LUTRAM的單位是64bit。

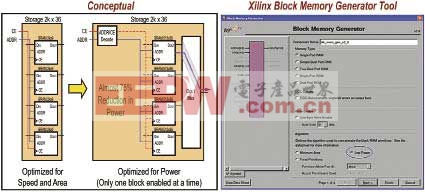

在這兩種類型中,BRAM通常功耗要大一些。啟用后的BRAM靜態功率是其功耗的最大部分,跳變帶來的功耗居于第二位。設計人員可以采取一些步驟來優化BRAM的功耗。例如,可以僅在讀或寫周期才啟用BRAM。對于較小的存儲器模塊可以使用LUTRAM來代替BRAM,將BRAM留給較大的存儲器模塊使用。此外,還可以嘗試將BRAM用于多個大型模塊。另一種技術是合理安排存儲器陣列來減少其占用的延遲面積、使性能最大化并盡量降低其功耗。圖1左側給出了一個針對速度和面積而優化的2K x 36bit存儲陣列。

我們利用四個2K x 9bit模塊并行構成這一存儲陣列,并在需要新值時啟用(Enable)所有四個模塊。另一方法是采用四個512 x 36bit模塊來安排2K x 36bit,但利用低兩位地址解碼來選擇訪問哪個512 x 36bit模塊。在后一種情況下,某個時間僅訪問一個存儲器塊,功耗將比第一種方法降低75%。

圖1右側顯示的是Xilinx公司的塊存儲器生成器(Block Memory Generator),利用它可以生成任意大小的存儲器陣列并可以針對速度或功率對其進行優化。圖2則給出了具體應用中的Xilinx Power Estimator,比較了在給定的使能速率下N個模塊同時啟動與N/4模塊啟動時的功耗情況。結果顯示動態功率降低了75%。

圖1 速度和面積與功率優化存儲器陣列(左)

以及Xilinx Block Memory Generator與功率面積選擇(右)

Xilinx工具可幫助選擇適合的存儲器陣列。考慮某個設計中需要兩組存儲器區域。一種情況下需要運行在300MHz的16組64 x 32bit存儲器結構(總位數為32K),另一種情況下需要16組512 x 36bit 存儲器架構 (總位數為294K)。

看一下16組64 x 32bit存儲器結構的功率比較,XPE工具顯示出小存儲器陣列最好用LUTRAM來實現,這樣比用BRAM節約85%的功耗(如圖3)。這是因為如果采用BRAM的話,只能用16個18K位的模塊來實現16個極小(64 x 32bit)的存儲器,有很多空間被浪費了。而第二種情況16組18K位陣列的功率比較,XPE顯示情況正好相反,應當采用大一些的存儲器陣列來實現(圖4)。這種情況下,采用BRAM比采用LUTRAM可以節約28%的功耗,這是因為如果采用LUTRAM就需要啟用更多的小粒度對象并增加更多的互連。

Xilinx FPGA的時鐘門控功能

Xilinx FPGA的時鐘門控功能提供了一些非常有意思的用途。例如,可以利用BUFGMUX時鐘緩沖器將FPGA內的某個全局時鐘關閉,或者動態選擇較慢的時鐘。還可以使用BUFGCE時鐘緩沖器進行按時鐘周期(cycle-by-cycle)的門控,與ASIC設計中使用的時鐘門控技術類似。設計中可以同時使用這兩種功能。