最新文章

Vivado HLS生成高效的處理流水線

在重構內核并生成解耦處理流水線的過程中,用來在不同階段移動數據的FIFO會形成很大開銷。通過復制少量計算指令可以去除一些FIFO,這樣通常很有好處,因為即使是最小深度的FIFO也會占用不少FPGA資源。

一般而言,在權衡利弊以探究最佳設計點的過程中,您可以使用成本模型和規范的優化技術。但在大多數基準測試中,僅僅為它的每個用戶復制簡單的循環計數器就可以節省很多面積,這也正是我們所做的。在這個引導性實例中, 該優化是指復制i的整數加法器,因此存儲結果 [i]時不需要從其它模塊獲得索引。

內存的突發訪問

第三項優化是內存的突發訪問(burst-memory access)。為了更高效地利用內存帶寬,我們希望通過一次內存事務處理攜帶多個數據字。

AXI總線協議允許您指定突發長度;而且,通過對解耦C函數進行一些小的修改,并利用流水線化的內存訪問模塊,我們就可利用該功能。

除了生成地址以外,解耦C函數中每個內存操作符還要在連續存儲塊被訪問時計算突發長度。循環計數器的復制還有助于突發訪問的生成,因為被訪問的字數量可以在每個解耦函數中本地確定。

實驗評估

我們應用上述方案做了幾個案例研究。 為評估這種方法的優勢,我們將使用該方案生成的解耦處理流水線 (DPP)與單純使用HLS生成的加速器進行比較。當為單純或DPP實現方案調用Vivado HLS時,我們將目標時鐘頻率設置到150MHz,并在布局布線后使用所能達到的最高時鐘速率。此外,我們針對加速器和內存子系統之間的交互嘗試了不同的機制。所用的端口為ACP和HP。我們為每個端口在可重配置陣列上實例化一個64KB高速緩存。

本實驗所用的物理器件是賽靈思的Zynq?-7000 XC7Z020全可編程SoC,安裝在ZedBoard評估平臺上。

我們還在Zynq SoC 的ARM?處理器上運行應用的軟件版本,并將其性能作為實驗的基準。生成的所有加速器功能齊全,無需任何DMA機制將數據移入和移出可重配置架構。

案例研究1:

背包問題

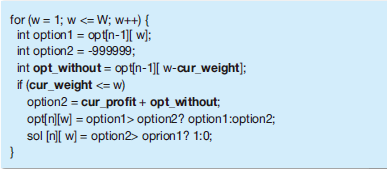

眾所周知,背包問題是一個組合問題,可以通過動態編程來求解。內核的結構如圖4所示。其中黑體字的變量都是在運行時間從內存讀取。

圖4 – 背包問題

圖4代碼:

for (w = 1; w <= W; w++) {

int option1 = opt[n-1][ w];

int option2 = -999999;

int opt_without = opt[n-1][ w-cur_weight];

if (cur_weight <= w)

option2 = cur_profit + opt_without;

opt[n][w] = option1> option2? option1:option2;

sol [n][ w] = option2> oprion1? 1:0;

}

因此,無法確切知道從哪個位置加載的變量opt_without。當w和n 比較大時,我們無法在片上緩沖整個opt陣列。

我們只能讓計算引擎取回所需的部分。

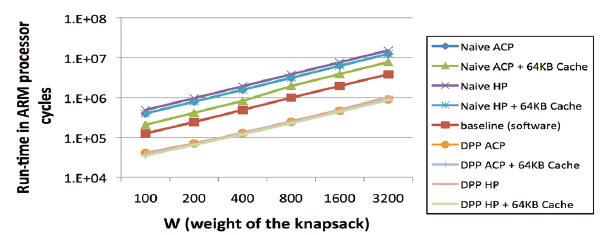

圖5給出了運行時間對比情況,將使用我們的方案(DPP)生成的加速器與單純通過HLS推送函數而生成的加速器進行比較。圖中還顯示了在ARM處理器上運行函數時的性能。

圖5 – 針對背包問題的運行時間比較

我們將n(項數)固定為40,使w (背包的總重量)在100至3,200之間變化。

從對比中很容易看出,通過單純使用Vivado HLS來映射軟件內核這種方法得到的加速器性能比基準要求慢很多。

Zynq SoC 上的超標量無序式ARM內核能很大程度開拓指令級并行性,而且具有一個高性能片上高速緩存。Vivado HLS工具提取的附加并行性顯然不足以補償硬處理器內核對于可編程邏輯的時鐘頻率優勢以及來自可重配置陣列的更長的數據訪問時延。

不過,當內核被解耦,分成多個處理階段時,性能就會明顯比ARM處理器性能高出約4.5倍。另外,當使用DPP時,各種內存訪問機制之間的差別相當小——使用我們的方案時,受內存訪問時延的影響要小很多。

案例研究2:稀疏矩陣向量乘法

稀疏矩陣向量(SpMV)乘法是一個計算內核,已經在各種研究項目中以很多不同方法進行過研究、變換和基準確定。這里,我們的目的不是使用特殊數據結構和存儲分配方式構建最佳性能的SpMV乘法,而是想根據最基本的算法描述看看在使用Vivado HLS時重構傳遞能提供多少優勢。

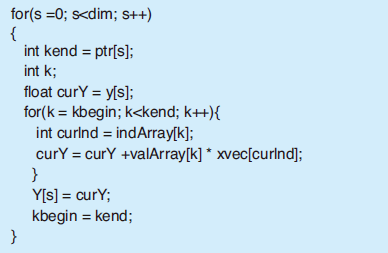

如圖6所示,在我們的實驗中,稀疏矩陣以壓縮稀疏行(CSR)格式存儲。在取回數字以進行實際的浮點乘法之前,需要先執行來自索引數組的負載。用來決定訪問哪個控制流程和內存位置的數值只有在運行時間才知道。

圖6 – 稀疏矩陣向量乘法

圖6代碼:

for(s =0; s<dim; s++)

{

int kend = ptr[s];

int k;

float curY = y[s];

for(k = kbegin; k<kend; k++){

int curlnd = indArray[k];

curY = curY +valArray[k] * xvec[curlnd];

}

Y[s] = curY;

kbegin = kend;

}

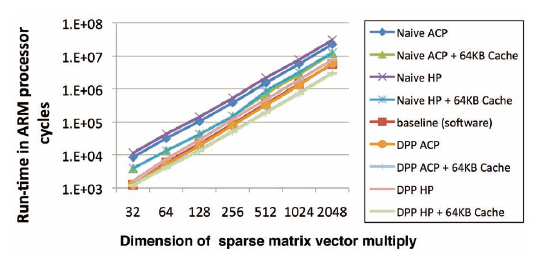

在圖7所示的運行時間對比中,矩陣的平均密度為1/16,尺寸在32和2,048之間變化。

圖7 – 針對稀疏矩陣向量乘法的運行時間對比

此處,單純的映射法在性能上再次落后于軟件版。當不使用FPGA上的高速緩存時,用我們的方法生成的解耦處理流水線在性能上幾乎與基準性能相同。

當在可重配置陣列上實例化一個64KB高速緩存時,DPP的性能接近基準的兩倍。與之前的基準相比,高速緩存的增加對DPP的性能具有更顯著的影響。

案例研究3:FLOYD-WARSHALL 算法

Floyd-Warshall是一種圖形算法,用來找到任意一對頂點之間成對的最短路徑。內存訪問模式比之前的基準要簡單。因此,有可能存在一種方法可以設計出DMA+加速器結構,以獲得很好的計算重疊和片外通信。我們的方案能試著自動實現這種重疊,但是我們尚未進行相關的研究,以表明絕對最佳與實際所得之間的差距。

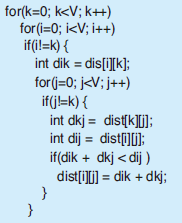

圖8 –Floyd-Warshall算法

圖8代碼:

for(k=0; k<V; k++)

for(i=0; i<V; i++)

if(i!=k) {

int dik = dis[i][k];

for(j=0; j<V; j++)

if(j!=k) {

int dkj = dist[k][j];

int dij = dist[i][j];

if(dik + dkj < dij )

dist[i][j] = dik + dkj;

}

}

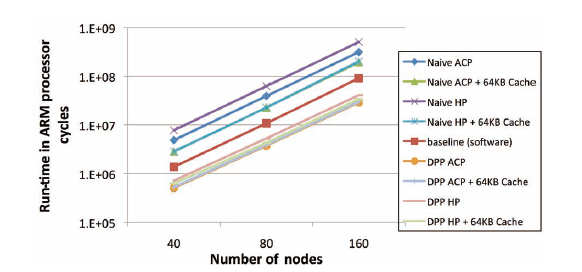

不過,與之前的基準一樣,我也進行了運行時間對比。這里,我們使圖形的大小在40個節點至160個節點之間變化。每個節點平均有全部節點的1/3作為其鄰點。

得到的結果與背包問題中的十分類似。

圖9 – 針對Floyd-Warshall算法的運行時間比較

解耦處理流水線所實現的性能約為軟件基準的3倍,吞吐量達到任何單純映射法的兩倍多。當使用DPP時,對FPGA高速緩存的影響也很小,展示出了對于內存訪問時延的容限。

我們這種簡單的技術構建出的處理流水線可以更好地使用內存帶寬,而且對內存時延有更好的容限,因此能夠改善Vivado HLS的性能。所描述的方法可對控制數據流圖中的內存訪問和較長的依賴循環解耦,這樣高速緩存缺失就不會拖延加速器的其它部分。