最新文章

賽靈思低功耗 FPGA與Algotronix MACsec內核

Algotronix采取了不同尋常的措施,即為所有許可的內核提供HDL源碼。這樣做的主要動機是支持客戶檢查,以便確保代碼不含病毒或特洛伊木馬代碼,而且不會強制進入非授權狀態或操作。有了源碼,就能降低客戶安全審核的成本和復雜性。此外,源碼可加速設計進程,因為工程師能夠方便地嘗試使用諸如加密、解密或加密/解密等不同配置參數和密鑰長度,并了解其各自仿真內核中的信號狀態。

數據中心內部通信可根據需要進行組織來分隔選定的機架,進而提供虛擬隔離區。這種功能可保護數據完整性,并應對數據中心和云應用中的隔離問題。無論是意外錯誤連接還是惡意行為(見圖4),MACsec系統都能檢測到未經認證的數據包,系統管理員可通過設置策略將其隔離或刪除。

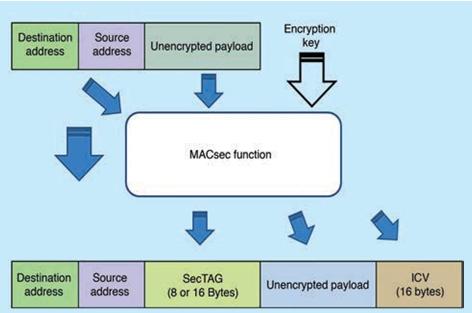

圖3 – MACsec幀結構包括MAC安全標簽(SecTAG)字段,其可定義EtherType,并標明數據包是否加密。

圖4 – MACsec將拒絕通過錯誤連接抵達的數據包,無論是因為意外情況造成還是惡意行為導致。

所有數據加密和解密都在端口級進行。除了附加的MACsec報頭和較少的額外時延,打開端口級加密不會增加開支,也不會對性能造成其它影響。

通過采用符合IEEE 802.1AE要求的加密Ethernet Lecel 2方案,設備廠商現在能用這些內核推動其系統特色化。基于云的用戶可能與其他用戶相互之間不信任,但他們現在設備制造商則能選擇可用的IP核來滿足1Gb和10 Gb以太網吞吐量的需求。

能夠從MACsec提供的數據機密大獲裨益,并且數據源認證功能可進一步保護他們的數據。

您可對內核進行配置,通過實現較寬的數據路徑來提高吞吐量,或通過選擇較窄的數據寬度來最大程度地減小FPGA封裝尺寸。擁有源碼還有其它更多優勢,包括更便于了解內核工作情況;也讓文檔記錄和歸檔變得更快捷方便。

此外,還配套提供了廣泛的驗證測試平臺,可幫助客戶在ModelSim等工具中確認操作是否正確。測試平臺包括MACsec的行為模型和MACsec IP核的自檢版本,能針對行為模型檢查可綜合硬件的輸出。這種自檢設計可在用戶仿真中實現實例化,便于測試實際用戶設計環境下的內核表現,并在錯誤驅動的情況下提供有用的診斷信息。

內核可提供許多選項,因此精確的資源數量將取決于您如何選擇參數,如數據速率、密鑰長度和所選SecY數量以及其它。然而,賽靈思網站IP部分列出的10G MACsec內核采用6,638個slice、20,916個LUT和53個BRAM塊。如需獲取許可證選項,敬請聯系Algotronix。

賽靈思低功耗 FPGA與Algotronix MACsec內核的完美結合為設備制造商實現產品差異化提供了高性能、低時延的解決方案。安全特性使得數據中心能夠確保其客戶機密,同時還可幫助安全管理員檢測并打擊惡意行為。