最新文章

XILINX賽靈思DSP系統(tǒng)生成器

Vivado系統(tǒng)生成器工具能方便地接入平臺(tái)設(shè)計(jì),從而可充分利用開發(fā)板接口和處理系統(tǒng)。

FPGA的應(yīng)用不斷拓展,同時(shí)FPGA設(shè)計(jì)流程也隨之不斷演進(jìn)。我們不再將FPGA用作簡(jiǎn)單的膠合邏輯,甚至不再作為信號(hào)處理鏈的核心,用以將IP與專有后端接口集成。相反,F(xiàn)PGA正在轉(zhuǎn)變?yōu)榭删幊唐舷到y(tǒng),其中包含作為處理器外設(shè)的硬件以及在強(qiáng)大APU上運(yùn)行的高級(jí)軟件。這種架構(gòu)就是我們所說的賽靈思全可編程SoC。

為了充分發(fā)揮這種全新流程的優(yōu)勢(shì),我們需要將設(shè)計(jì)方法從FPGA早期的自上而下RTL轉(zhuǎn)變?yōu)橐訧P開發(fā)和標(biāo)準(zhǔn)化連接(例如ARM?的高級(jí)可擴(kuò)展接口 (AXI))為中心的自下而上流程。隨著接口從定制接口發(fā)展為通用接口,我們就可以花更少的精力來驗(yàn)證數(shù)據(jù)路徑與平臺(tái)設(shè)計(jì)之間的交互。

賽靈思DSP系統(tǒng)生成器(System Generator for DSP)同樣也得到了發(fā)展。該工具是Vivado?設(shè)計(jì)套件的一部分,其通過將DSP數(shù)據(jù)路徑整合到用Vivado IP Integrator工具構(gòu)建的平臺(tái)設(shè)計(jì)中,打造出全新的自下而上設(shè)計(jì)方法。我們仔細(xì)看看系統(tǒng)生成器(System Generator)實(shí)現(xiàn)的設(shè)計(jì)自動(dòng)化如何幫助高性能設(shè)計(jì)充分利用平臺(tái)連接功能。

構(gòu)建全可編程平臺(tái)框架

通過定義用來存放數(shù)據(jù)路徑的平臺(tái)框架,我們可以啟動(dòng)全新的設(shè)計(jì)流程。Vivado工具套件能識(shí)別開發(fā)板;我們將利用開發(fā)板自動(dòng)化功能構(gòu)建新的平臺(tái)設(shè)計(jì)。

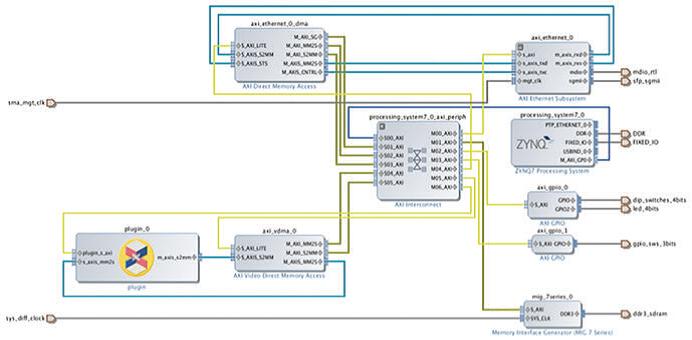

如圖1所示,平臺(tái)設(shè)計(jì)或平臺(tái)框架的基本組成包括:處理器級(jí)和開發(fā)板級(jí)接口,以及將其組合在一起的邏輯。我們將平臺(tái)框架作為系統(tǒng)級(jí)設(shè)計(jì)的基礎(chǔ)(即外殼),這給我們的數(shù)據(jù)路徑提供了空間。模塊和連接功能自動(dòng)化通過IP外設(shè)將處理系統(tǒng)連接到板級(jí)接口。封裝在IP Catalog中的DSP數(shù)據(jù)路徑或軟件加速器利用賽靈思Designer Assistance自動(dòng)化功能方便地連接到我們的處理器平臺(tái)框架中,進(jìn)而連接到外部器件接口。

圖1 –將處理系統(tǒng)連接到板級(jí)接口的平臺(tái)框架實(shí)例

創(chuàng)建作為可輸入IP的數(shù)據(jù)路徑

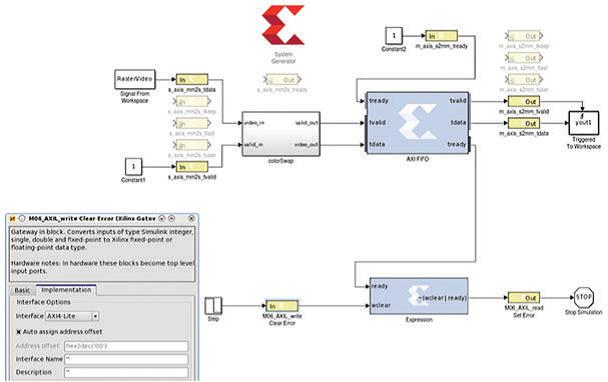

我們的最終目標(biāo)是讓數(shù)據(jù)路徑能進(jìn)入全可編程平臺(tái)框架。如果要從頭開始,我們可以用標(biāo)準(zhǔn)化接口創(chuàng)建數(shù)據(jù)路徑。如圖2所示,只需將網(wǎng)關(guān)端口迅速標(biāo)記為AXI4-Lite接口,或者對(duì)端口進(jìn)行命名以匹配標(biāo)準(zhǔn)連接(如Simulink?圖上的AXI4-Stream),這樣,System Generator為Vivado IP Catalog打包設(shè)計(jì)時(shí)就會(huì)為設(shè)計(jì)添加額外邏輯并將通用信號(hào)收集到接口內(nèi)。

圖2 – 自動(dòng)將網(wǎng)關(guān)導(dǎo)入AXI4-Lite和AXI4-Stream接口

不過,我們利用一種新設(shè)計(jì)方法,使用平臺(tái)框架定制一個(gè)可集成到全可編程設(shè)計(jì)的插件。我們使用自動(dòng)化功能確定平臺(tái)設(shè)計(jì)中現(xiàn)有哪些接口,哪些接口與開發(fā)板關(guān)聯(lián),以及哪些接口可為DSP數(shù)據(jù)路徑創(chuàng)建插件。既然我們的目標(biāo)是將數(shù)據(jù)路徑轉(zhuǎn)換為可連接至平臺(tái)框架的IP,因此我們不需要關(guān)注板級(jí)接口,而是關(guān)注標(biāo)準(zhǔn)化AXI接口。開發(fā)板上的每個(gè)不關(guān)聯(lián)接口轉(zhuǎn)變?yōu)镾ystem Generator網(wǎng)關(guān)。這些網(wǎng)關(guān)在System Generator中充當(dāng)簡(jiǎn)單信號(hào),當(dāng)我們將平臺(tái)設(shè)計(jì)導(dǎo)出到IP Catalog時(shí),這些網(wǎng)關(guān)會(huì)生成用以連接平臺(tái)設(shè)計(jì)的AXI 接口。

如實(shí)例所示,AXI4-Lite接口創(chuàng)建獨(dú)立的讀/寫信號(hào),在導(dǎo)出到Vivado工具套件時(shí)共享通用的可尋址寄存器接口。簡(jiǎn)單的復(fù)制-粘貼使我們?cè)诘刂菲莆恢猛ㄟ^相同接口獲得更多用于處理器的直接寄存器。同時(shí),我們可自動(dòng)生成軟件驅(qū)動(dòng)API以讀/寫寄存器。

如果平臺(tái)設(shè)計(jì)中提供AXI4-Stream接口,System Generator會(huì)向模型添加正確匹配的網(wǎng)關(guān)。AXI4- Stream接口極其靈活并包含很多信號(hào)。ACLK時(shí)鐘源與該接口相關(guān)聯(lián),但該信號(hào)直接作為這部分?jǐn)?shù)據(jù)路徑的抽象系統(tǒng)時(shí)鐘。TVALID信號(hào)表示接口有效。其他信號(hào)為可選信號(hào)。System Generator會(huì)將初始流接口中的信號(hào)添加到我們的模型,不過我們可以通過刪除或添加信號(hào)來滿足內(nèi)部要求。

在圖2所示的模型中,我們的數(shù)據(jù)路徑只關(guān)心TDATA(經(jīng)接口發(fā)送的數(shù)據(jù))和S_AXIS接口上的TVALID。為刪除不必要的信號(hào),我們針對(duì)該模型對(duì)沒用的網(wǎng)關(guān)添加注釋,因?yàn)槟J(rèn)值將會(huì)驅(qū)動(dòng)IP Integrator中的信號(hào)連接。

AXI4-Lite和AXI4-Stream信號(hào)能利用自下而上方法輕松進(jìn)行仿真和驗(yàn)證。AXI4-Lite接口建模為用于訪問大量Simulink模塊的簡(jiǎn)單網(wǎng)關(guān),實(shí)現(xiàn)網(wǎng)關(guān)一側(cè)到另一側(cè)數(shù)據(jù)傳送的抽象。同樣,AXI4-Stream接口只是一系列遵循簡(jiǎn)單握手規(guī)則的信號(hào),以將數(shù)據(jù)從一個(gè)IP核傳遞到另一個(gè)。

仿真建模的唯一挑戰(zhàn)在于接口上所用的可選端口。如果我們每個(gè)周期都接收數(shù)據(jù)并通過數(shù)據(jù)路徑無中斷地進(jìn)行處理,我們就不需要TREADY握手信號(hào)。簡(jiǎn)化模型通過TDATA 網(wǎng)關(guān)將矢量的每個(gè)元素從Simulink的信號(hào)發(fā)送到Workspace令牌。當(dāng)需要完整握手時(shí),我們用AXI4-Stream FIFO進(jìn)行建模以緩沖數(shù)據(jù),如圖2中的M_AXIS接口所示。

這種定制的自動(dòng)化功能可作為創(chuàng)建連接平臺(tái)框架的IP的起點(diǎn)。不過,System Generator很靈活,允許我們添加或刪除部分甚至整個(gè)AXI接口。最終可將數(shù)據(jù)路徑轉(zhuǎn)換為可在多個(gè)系統(tǒng)級(jí)設(shè)計(jì)中重用的IP。

添加邏輯后,最后一步是將使用DSP系統(tǒng)生成器構(gòu)建的數(shù)據(jù)路徑導(dǎo)出到Vivado IP Catalog。這種操作能實(shí)現(xiàn)接口的簡(jiǎn)單連接,無論使用RTL還是在IP Integrator中都是如此。此外,我們還生成在SDK中使用的驅(qū)動(dòng)器,并將具有最佳測(cè)試向量數(shù)據(jù)的仿真模型連接到IP。由于我們?cè)趧?chuàng)建DSP數(shù)據(jù)路徑時(shí)事先知道平臺(tái)框架的情況,因此能自動(dòng)組合模型和平臺(tái)設(shè)計(jì),如圖3中的完整系統(tǒng)所示。

圖3 – 將DSP數(shù)據(jù)路徑連接到平臺(tái)框架的平臺(tái)系統(tǒng)

降低仿真風(fēng)險(xiǎn)

生成包含硬件加速器、DSP數(shù)據(jù)路徑或定制邏輯的完整片上系統(tǒng)很具有挑戰(zhàn)性。采用自下而上方式進(jìn)行仿真以確定數(shù)據(jù)路徑按預(yù)期工作,這種方法風(fēng)險(xiǎn)很大,而且維持可支持?jǐn)?shù)據(jù)路徑的平臺(tái)接口帶寬同樣很困難。

===========================================

深圳市毅創(chuàng)騰電子科技有限公司

電話:(86)-755-83210909 83616256 83210801 83213361

企業(yè)QQ: 2355507165 / 2355507163

網(wǎng)址:www.zjaotaijx.cn

===========================================

毅創(chuàng)騰電子科技有限公司是一家大型、專業(yè)的XILINX(賽靈思)、ALTERA(阿特拉)、FREESCALE(飛思卡爾)、ADI嵌入式FPGA、CPLD、微控制器等集成電路銷售與服務(wù)的授權(quán)分銷商。也是亞太地區(qū)最大規(guī)模的原裝XILINX、ALTERA、FREESCALE產(chǎn)品供應(yīng)商之一。

分銷商,原裝熱賣中,ALTERA XILINX專線:0755-83210909專業(yè)銷售嵌入式FPGA現(xiàn)場(chǎng)可編程器件,主要以XILINX,ALTERA為核心的專業(yè)分銷商。

===========================================